半加器与全加器

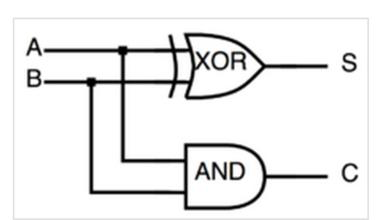

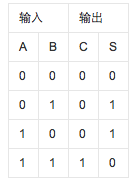

半加器:

半加器电路是指对两个输入数据位相加,输出一个结果位和进位,没有进位输入的加法器电路。 是实现两个一位二进制数的加法运算电路。

逻辑图:

真值表:

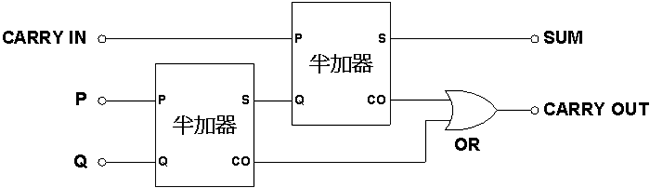

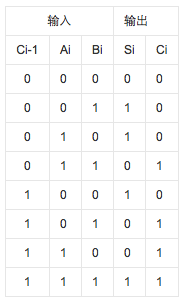

全加器:

全加器英语名称为full-adder,是用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。一位全加器可以处理低位进位,并输出本位加法进位。多个一位全加器进行级联可以得到多位全加器。

逻辑图:

真值表:

半加器与全加器

https://slw.im/2016/11/half-adder-and-full-adder/